- Basic Electronics Tutorial

- Electronic Components

Enhancement Mode Fet Symbol

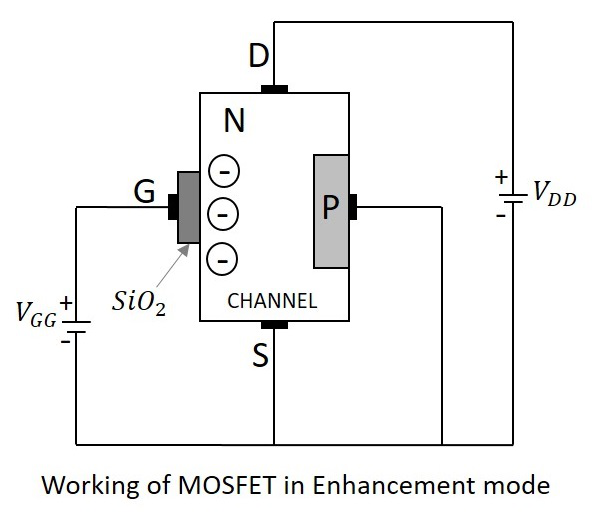

Let's take a look inside an N-channel device.http://www.sciencewriter.net. Enhancement Type; Depletion Type Enhancement Mode MOSFET Transistor. In Enhancement-mode MOSFET or eMOSFET, the conducting channels are doped to a level so that it becomes non-conductive. This results in a transistor that no conduction at zero voltage. The term enhancement mode refers to the influence of the gate voltage in enhancing the conductivity of the channel. The term field effect refers to the effect of the electric field from gate to bulk that is associated with the gate voltage. The mode can be determined by the sign of the threshold voltage (gate voltage relative to source voltage at the point where an inversion layer just forms in the channel): for an N-type FET, enhancement-mode devices have positive thresholds, and depletion-mode devices have negative thresholds; for a P-type FET, enhancement-mode negative.

- Resistors

- Capacitors

- Inductors

- Transformers

- Diodes

- Transistors

- Basic Electronics Useful Resources

- Selected Reading

The JFET is abbreviated as Junction Field Effect Transistor. JFET is just like a normal FET. The types of JFET are n-channel FET and P-channel FET. A p-type material is added to the n-type substrate in n-channel FET, whereas an n-type material is added to the ptype substrate in p-channel FET. Hence it is enough to discuss one type of FET to understand both.

N-Channel FET

The N-channel FET is the mostly used Field Effect Transistor. For the fabrication of Nchannel FET, a narrow bar of N-type semiconductor is taken on which P-type material is formed by diffusion on the opposite sides. These two sides are joined to draw a single connection for gate terminal. This can be understood from the following figure.

These two gate depositions (p-type materials) form two PN diodes. The area between gates is called as a channel. The majority carriers pass through this channel. Hence the cross sectional form of the FET is understood as the following figure.

Ohmic contacts are made at the two ends of the n-type semiconductor bar, which form the source and the drain. The source and the drain terminals may be interchanged.

Operation of N-channel FET

Before going into the operation of the FET one should understand how the depletion layers are formed. For this, let us suppose that the voltage at gate terminal say VGG is reverse biased while the voltage at drain terminal say VDD is not applied. Let this be the case 1.

In case 1, When VGG is reverse biased and VDD is not applied, the depletion regions between P and N layers tend to expand. This happens as the negative voltage applied, attracts the holes from the p-type layer towards the gate terminal.

In case 2, When VDD is applied (positive terminal to drain and negative terminal to source) and VGG is not applied, the electrons flow from source to drain which constitute the drain current ID.

Let us now consider the following figure, to understand what happens when both the supplies are given.

The supply at gate terminal makes the depletion layer grow and the voltage at drain terminal allows the drain current from source to drain terminal. Suppose the point at source terminal is B and the point at drain terminal is A, then the resistance of the channel will be such that the voltage drop at the terminal A is greater than the voltage drop at the terminal B. Which means,

VA>VB

Hence the voltage drop is being progressive through the length of the channel. So, the reverse biasing effect is stronger at drain terminal than at the source terminal. This is why the depletion layer tends to penetrate more into the channel at point A than at point B, when both VGG and VDD are applied. The following figure explains this.

Now that we have understood the behavior of FET, let us go through the real operation of FET.

Depletion Mode of Operation

As the width of depletion layer plays an important role in the operation of FET, the name depletion mode of operation implies. We have another mode called enhancement mode of operation, which will be discussed in the operation of MOSFETs. But JFETs have only depletion mode of operation.

Let us consider that there is no potential applied between gate and source terminals and a potential VDD is applied between drain and source. Now, a current ID flows from drain to source terminal, at its maximum as the channel width is more. Let the voltage applied between gate and source terminal VGG is reverse biased. This increases the depletion width, as discussed above. As the layers grow, the cross-section of the channel decreases and hence the drain current ID also decreases.

When this drain current is further increased, a stage occurs where both the depletion layers touch each other, and prevent the current ID flow. This is clearly shown in the following figure.

The voltage at which both these depletion layers literally “touch” is called as “Pinch off voltage”. It is indicated as VP. The drain current is literally nil at this point. Hence the drain current is a function of reverse bias voltage at gate.

Since gate voltage controls the drain current, FET is called as the voltage controlled device. This is more clearly understood from the drain characteristics curve.

Enhancement Mode Fet

Drain Characteristics of JFET

Let us try to summarize the function of FET through which we can obtain the characteristic curve for drain of FET. The circuit of FET to obtain these characteristics is given below.

When the voltage between gate and source VGS is zero, or they are shorted, the current ID from source to drain is also nil as there is no VDS applied. As the voltage between drain and source VDS is increased, the current flow ID from source to drain increases. This increase in current is linear up to a certain point A, known as Knee Voltage.

The gate terminals will be under reverse biased condition and as ID increases, the depletion regions tend to constrict. This constriction is unequal in length making these regions come closer at drain and farther at drain, which leads to pinch off voltage. The pinch off voltage is defined as the minimum drain to source voltage where the drain current approaches a constant value (saturation value). The point at which this pinch off voltage occurs is called as Pinch off point, denoted as B.

As VDS is further increased, the channel resistance also increases in such a way that ID practically remains constant. The region BC is known as saturation region or amplifier region. All these along with the points A, B and C are plotted in the graph below.

The drain characteristics are plotted for drain current ID against drain source voltage VDS for different values of gate source voltage VGS. The overall drain characteristics for such various input voltages is as given under.

As the negative gate voltage controls the drain current, FET is called as a Voltage controlled device. The drain characteristics indicate the performance of a FET. The drain characteristics plotted above are used to obtain the values of Drain resistance, Transconductance and Amplification Factor.

In field-effect transistors (FETS), depletion mode and enhancement mode are two major transistor types, corresponding to whether the transistor is in an ON state or an OFF state at zero gate-source voltage.

Enhancement-mode MOSFETS (metal–oxide–semiconductor FETs) are the common switching elements in most integrated circuits. These devices are off at zero gate–source voltage. NMOS can be turned on by pulling the gate voltage higher than the source voltage, PMOS can be turned on by pulling the gate voltage lower than the source voltage. In most circuits, this means pulling an enhancement-mode MOSFET's gate voltage towards its drain voltage turns it ON.

In a depletion-mode MOSFET, the device is normally ON at zero gate–source voltage. Such devices are used as load 'resistors' in logic circuits (in depletion-load NMOS logic, for example). For N-type depletion-load devices, the threshold voltage might be about –3 V, so it could be turned off by pulling the gate 3 V negative (the drain, by comparison, is more positive than the source in NMOS). In PMOS, the polarities are reversed.

The mode can be determined by the sign of the threshold voltage (gate voltage relative to source voltage at the point where an inversion layer just forms in the channel): for an N-type FET, enhancement-mode devices have positive thresholds, and depletion-mode devices have negative thresholds; for a P-type FET, enhancement-mode negative, depletion-mode positive.

| NMOS | PMOS | |

|---|---|---|

| Enhancement-mode | Vd > Vs (typ) ON: Vg ≥ Vs + 3V OFF: Vg ≤ Vs | Vd < Vs (typ) ON: Vg ≤ Vs - 3V OFF: Vg ≥ Vs |

| Depletion-mode | Vd > Vs (typ) ON: Vg ≥ Vs OFF: Vg ≤ Vs - 3V | Vd < Vs (typ) ON: Vg ≤ Vs OFF: Vg ≥ Vs + 3V |

Junction field effect - transistors (JFETs) are depletion mode, since the gate junction would forward bias if the gate were taken more than a little from source toward drain voltage. Such devices are used in gallium arsenide and germanium chips, where it is difficult to make an oxide insulator.

Alternative terminology[edit]

Some sources say 'depletion type' and 'enhancement type' for the device types as described in this article as 'depletion mode' and 'enhancement mode', and apply the 'mode' terms for which direction the gate–source voltage differs from zero.[1] Moving the gate voltage toward the drain voltage 'enhances' the conduction in the channel, so this defines the enhancement mode of operation, while moving the gate away from the drain depletes the channel, so this defines depletion mode.

Enhancement-load and depletion-load logic families[edit]

Depletion-load NMOS logic refers to the logic family that became dominant in silicon VLSI in the latter half of the 1970s; the process supported both enhancement-mode and depletion-mode transistors, and typical logic circuits used enhancement-mode devices as pull-down switches and depletion-mode devices as loads, or pull-ups. Logic families built in older processes that did not support depletion-mode transistors were retrospectively referred to as enhancement-load logic, or as saturated-load logic, since the enhancement-mode transistors were typically connected with gate to the VDD supply and operated in the saturation region (sometimes the gates are biased to a higher VGG voltage and operated in the linear region, for a better power–delay product (PDP), but the loads then take more area).[2] Alternatively, rather than static logic gates, dynamic logic such as four-phase logic was sometimes used in processes that did not have depletion-mode transistors available.

For example, the 1971 Intel 4004 used enhancement-load silicon-gate PMOS logic, and the 1976 Zilog Z80 used depletion-load silicon-gate NMOS.

History[edit]

The first MOSFET (metal-oxide-semiconductor field-effect transistor) demonstrated by Egyptian engineer Mohamed M. Atalla and Korean engineer Dawon Kahng at Bell Labs in 1960 was an enhancement mode siliconsemiconductor device.[3] In 1963, both depletion and enhancement mode MOSFETs were described by Steve R. Hofstein and Fred P. Heiman at RCA Laboratories.[4] In 1966, T.P. Brody and H.E. Kunig at Westinghouse Electric fabricated enhancement and depletion mode indium arsenide (InAs) MOS thin-film transistors (TFTs).[5][6]

References[edit]

- ^John J. Adams (2001). Mastering Electronics Workbench. McGraw-Hill Professional. p. 192. ISBN978-0-07-134483-8.

- ^Jerry C. Whitaker (2005). Microelectronics (2nd ed.). CRC Press. p. 6-7–6-10. ISBN978-0-8493-3391-0.

- ^Sah, Chih-Tang (October 1988). 'Evolution of the MOS transistor-from conception to VLSI'(PDF). Proceedings of the IEEE. 76 (10): 1280–1326 (1293). doi:10.1109/5.16328. ISSN0018-9219.

- ^Hofstein, Steve R.; Heiman, Fred P. (September 1963). 'The silicon insulated-gate field-effect transistor'. Proceedings of the IEEE. 51 (9): 1190–1202. doi:10.1109/PROC.1963.2488.

- ^Woodall, Jerry M. (2010). Fundamentals of III-V Semiconductor MOSFETs. Springer Science & Business Media. pp. 2–3. ISBN9781441915474.

- ^Brody, T. P.; Kunig, H. E. (October 1966). 'A HIGH‐GAIN InAs THIN‐FILM TRANSISTOR'. Applied Physics Letters. 9 (7): 259–260. doi:10.1063/1.1754740. ISSN0003-6951.